# Designing a Semiconductor Characterization System for an Undergraduate Fabrication Lab

#### Introduction

Virginia Polytechnic Institute and State University recently opened an 1,800 sq. ft. Class 10,000 cleanroom. This cleanroom is designed to help undergraduates learn the elements of the microchip fabrication process over the course of one semester and to encourage them to pursue more advanced studies. Unlike programs based on the use of tightly controlled IC production processes as teaching tools, the equipment used encourages students to experiment to find out how far they can "push" a specific processing tolerance before it affects device parameters. As part of their coursework, students learn how to measure the surface resistivity (i.e., sheet resistance) of test regions on a wafer during processing and to perform I-V characterization of the devices they create, which include capacitors, p-n junction diodes, resistors, and nMOSFETs [1]. This case study describes a simple, cost-effective parameter analysis system, built of easily obtainable components and programmed using a commercial, off-the-shelf test and measurement automation programming environment.

## Requirements

To address the needs of this high throughput undergraduate laboratory, the semiconductor characterization system had to meet several requirements:

- It had to be relatively inexpensive.

- It had to allow students to determine:

- the surface resistivities of doped and as-received wafers, and

- I–V curves of semiconductor resistors, p-n junctions, FETs, and other devices that may be created in the laboratory.

- It had to make measurements on devices with dimensions in the range of hundreds of microns.

- The results it generated should correlate well with those obtained using more sophisticated systems.

- It should allow students to minimize the time invested in learning how to make measurements so they can spend more time analyzing the results of those measurements. The system must be fully automated to make this possible.

- It had to provide a simple method of data export so that results can be included

in lab reports. To prevent a common source of contamination, protocols prohibit

bringing paper and floppy disks into the cleanroom, so the system had to be

capable of linking to a file server.

- To simplify system maintenance and upgrades, a simple, well-established, high level programming language had to be used to create the application software.

# **System Description**

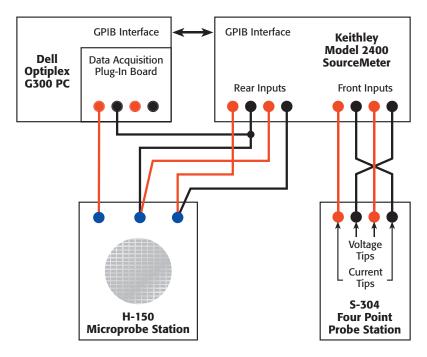

The system includes a dedicated four-point probe station for surface resistivity measurements and a wafer probe station with micromanipulators for all I-V measurements. To ensure proper characterization, both stations are protected by a dark box to prevent photosensitive materials or devices from generating photocurrents if struck by the ambient light. The system also includes a voltage/current source and a dedicated PC for data acquisition. The measurement instruments are connected to the PC via GPIB; all programming is performed using the automation software.

# System components include:

- Keithley Instruments Model 2400 SourceMeter® instrument [2].

- Signatone S-304-4 Four Point Probe Station [3] with SP4-62.5-85-TC probe head.

- Signatone H-150 Hybrid Microprobe Station [3] with six micromanipulation probes.

- Data acquisition board with A/D, D/A capability and a shielded I/O connector block.

- Custom-made dark box [4].

- Dell Optiplex G300 PC (550MHz processor, 128MB memory, 10GB HD, Ethernet NIC) with Microsoft Windows 2000 Pro operating system [5].

- GPIB card for the PC.

- Miscellaneous cabling.

Figure 1. Virginia Tech's semiconductor characterization system. Components from left to right: Keithley Model 2400, Signatone S-304, Signatone H-150, and Dell PC. The system instrumentation is protected with a dark box, shown here with the cover raised.

The Model 2400 SourceMeter instrument has front and rear panel dual outputs, which allow connecting both the S-304 and the H-150 to the Model 2400 simultaneously, although only one may be used at any given time. The system's wiring is straightforward (*Figure 2*).

Figure 2. Schematic of Virginia Tech's semiconductor characterization system.

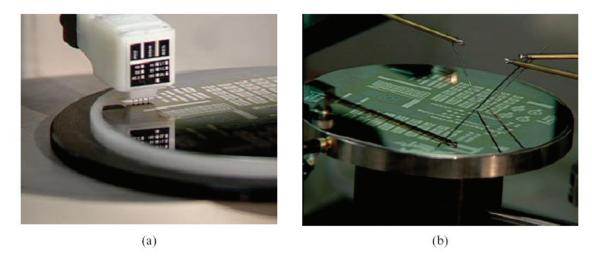

The Model 2400's front panel I/O outputs are connected to the outer current probe tips of the S-304's surface resistivity four-point probes, while the front panel four-wire sense inputs are connected to the inner voltage probe tips. When the system is used to measure surface resistivity, the data acquisition board's (DAQ) voltage source isn't used. In the case of the H-150 microprobe station, the Model 2400's two rear panel I/O outputs, as well as the data acquisition voltage output, are connected to three micromanipulator probe tips that are positioned appropriately on the device under test (DUT) for the given device and measurement. The Model 2400 is controlled by software via the GPIB interface while the data acquisition board is programmed directly. *Figure 3* shows two wafers under test, one in the four-point probe station and one in the microprobe station.

Figure 3: Photos of DUT (a) in the four-point probe station, and (b) in the microprobe station.

If exposed to the yellow fluorescent light in the fabrication facility, the wafers would generate photocurrents that would degrade measurement quality significantly. To prevent this problem, Virginia Tech designed a simple dark box built from black polypropylene [4]. As *Figure 1* shows, this box has a cover that lifts to allow access to both probe stations but ensures total darkness when closed.

#### **Software Requirements and Design**

The system's hardware is powerful and capable of performing all the tests required for the laboratory experiments. Without the use of automation, while it's possible to complete the tests required to characterize both the process and the resulting devices fully, it's extremely tedious. Therefore, Virginia Tech developed a complete computer control system that enhances ease of use and allows recording and analysis of the data gathered in each test. For applications of this type, the system control code must interface easily with the hardware, must allow for some manipulation of test parameters (but not necessarily the actual setup of those tests), and must support storing and exporting the data gathered in a format that allows it to be manipulated by other analysis programs (curve fitting software, Microsoft Excel, etc.). The semiconductor fabrication facility is an evolving laboratory, so the ability to modify the software easily if there are changes to the devices or the process flow is essential.

The theory underlying the various tests (surface resistivity for process control and I–V curves of resistors, p-n junction diodes, and nMOSFETs) has been described extensively in

the technical literature. We have closely followed the texts of Schroder [6], Neudeck [7], and Pierret [8], as well as the relevant ASTM standard procedures [9, 10].

The characterization system must automate the data acquisition necessary for each measurement, and show the basic I–V characteristics for each measurement. To gain the appropriate experience, students must also be able to perform data manipulation, curve fitting, and parameter extraction manually, using software that's not part of the characterization system. Although all of these analyses can be performed in Microsoft Excel, the availability of a set of statistical macros is especially valuable for more advanced students, who are required to perform error analyses on the parameters they extract from the system.

The characterization system includes a simple graphical user interface (GUI) that leads the student through the measurements. First, the student selects the type of measurement to be performed and the system instructs the student to mount the wafer in the correct station and position the requisite probes (either four-point surface resistivity or I–V measurements using micromanipulators) on the location/device to be measured. In the case of I–V measurements, the student is instructed to position either two probes (resistors, pn junctions) or three probes (FETs). The dark box lid is closed and the PC is instructed to proceed.

## **Applications**

Four tests that are performed routinely in the lab are designed into the characterization system:

- Measurement of the surface resistivity of the wafer following various steps in the processing.

- I–V characteristics of resistors.

- I–V characteristics of pn junction diodes.

- I–V characteristics of nMOSFETs.

More tests can be added when new devices are included in the mask set the students use. In the future, it might be possible to build contact resistance structures, capacitors, BJTs, pMOSFETs, cMOSFETs, and possibly simple circuits such as ring oscillators and simple logic circuits. However, for the present, the three devices now on the mask set provide an excellent introduction to MOS fabrication for sophomores.

### 1) Surface Resistivity

The resistivity of a finite slab of a uniformly doped semiconductor wafer is determined by the four-point probe method with uniformly spaced probes [11]. The surface resistivity is an averaged measurement of the number of carriers present in a diffused wafer.

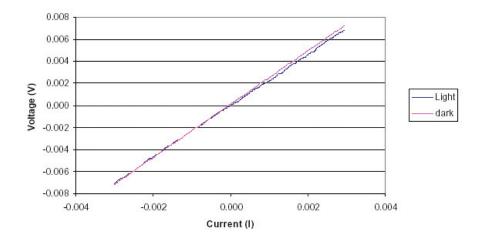

To measure surface resistivity, a small, fixed current is applied to the outer pair of probes and the potential across the inner pair of probes is measured following the ASTM standard procedure [9]. In the apparatus, the drive current is swept between lower and upper limits that result in induced voltages of approximately –10mV and 10mV respectively. *Figure 4* shows a typical result for a sample wafer. The two curves in the figure show the sensitivity of the measurement to light. These curves represent the raw data measured by sweeping a DC current source and measuring the resulting DC voltage. The starting voltage, ending voltage, number of points to measure, and horizontal correction factor are all user-inputs into the system. The starting and ending voltages are selected in accordance with the ASTM standard procedure [9]. Once data acquisition is complete, a regression curve is fitted through the data to determine V/I, and the surface resistivity is computed.

This measurement approach deviates from the ASTM standard procedure in two important aspects. First, rather than measuring the voltage at a fixed drive current and then with the current leads reversed, and then averaging the two results, Virginia Tech's automated system sweeps the drive current between the negative and positive values (as shown in *Figure 4*) and computes a regression line fit to the data. This is equivalent to performing the average n times, where 2n + 1 is the number of data points in the sweep. Second, the ASTM procedure requires determining the drive current by placing a standard resistor in series with the current probes and measuring the voltage drop across it with a  $3\frac{1}{2}$ -digit voltmeter. In Virginia Tech's system, the output current is programmed, but the actual current output by the Model 2400 is read back. With the SourceMeter instrument's  $5\frac{1}{2}$ -digit resolution, this procedure provides excellent results. More importantly, it greatly simplifies the measurements and reduces the system's cost.

Figure 4. Example of  $R_s$  data generated by the characterization system and plotted in Microsoft Excel. Note the increase in the current resulting from photogeneration when the sample is measured in the light. The effect of light is to reduce  $R_s$  from its correct value by 3%.

Surface resistivity is measured throughout the wafer fabrication process to ensure proper doping, as well as to monitor the effect of thermal cycling on dopant redistribution to some degree [1].

#### 2) Resistors

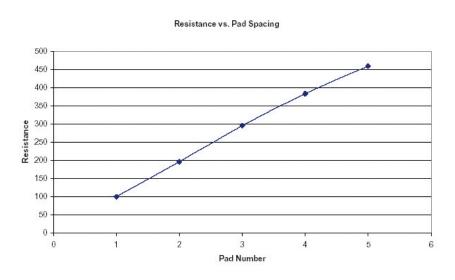

When wafer fabrication is complete, the first devices characterized are the resistors. Resistors are made from n-diffused lines ( $N_D = 10^{17}/cc - 10^{19}/cc$ ) in the p-type substrate (NA =  $10^{14}/cc$ ). They are created as circuitous signal paths with multiple metallic pads, as shown in *Figure 5*. This geometry is designed to allow the students to check the uniformity of long resistors by measuring the resistance between different pads. The resistance between any two pads (numbered 0,1,...,5, respectively) is measured by mounting the wafer on the H-150 microprobe station, positioning one probe on pad 0, and the other probe sequentially on pads 1 through 5.

Figure 5. Typical layout of a resistor. The black rectangles represent Al measurement contact pads.

The GUI instructs the user to input a starting voltage, a stopping voltage, and the number of points to sweep. The system then sweeps the voltage through those values and measures the resulting current. A regression plot of the sensed voltage vs. the drive current gives a straight line with a slope that is the resistance between the probes. These data are saved for export and further off-line data analysis.

Since the geometry of the resistors is identical for each segment of the resistor's signal path, and if the wafer is uniformly doped over the physical size of the entire resistor, the resistance between each pair of pads should be identical. Under these conditions, a plot of the resistance from pad zero to the nth pad should be a straight line, as shown in *Figure 6*.

It is possible to compute the surface resistivity of the material from these data. The data for this resistor's signal path agree well with the surface resistivity measured as described in the previous section, thus confirming the uniformity of doping of the wafer during processing.

Figure 6. Plot of resistance vs. pad spacing. The graph is linear which implies locally uniform doping of the substrate over the dimensions of the resistor.

## 3) p-n Junctions

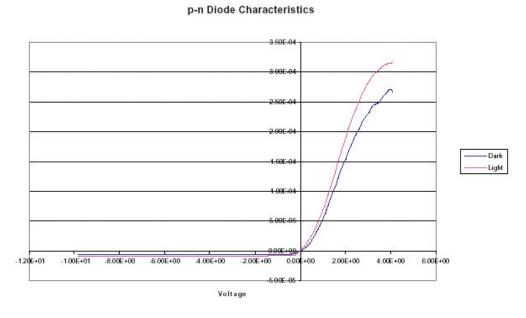

The p-n junction devices are constructed by creating an n+ well in the p-type substrate by thermal diffusion [1]. A thin (40nm) layer of gate oxide is grown over both the p-type substrate and the n-well to provide physical protection. Next, an aluminum contact pad (50nm) is evaporated on each side of the p-n junction, contacting the silicon through holes chemically etched through the oxide. The I–V characteristics of the p-n junctions may therefore be thought of as surface measurements. For this reason, all characterization will follow the analysis of the abrupt junction diode [7]. *Figure 7* shows a typical I–V curve for a diode junction, including both the case in which there is direct light on the diode and the case in which the diode is protected in the dark box. This plot shows a significant photoelectric effect on the measurements. The reverse bias current is raised from –5mA to –8mA for light vs. dark conditions.

Figure 7. Example of light vs. dark measurements for a typical p-n junction diode. Reverse currents for light and dark measurements are -8μA and -5μA respectively. Also note the difference in slope of the 'on' sections of the curves.

The students routinely examine three characteristics of the p-n junction using this setup—the reverse breakdown voltage, the ideality factor, and the effect of the bulk semiconductor resistance on the forward current.

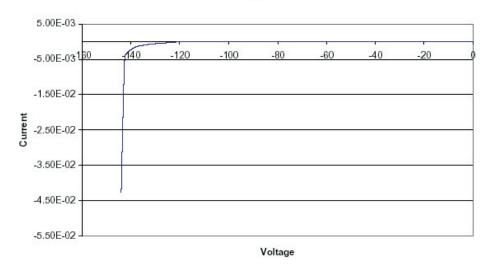

#### Reverse Breakdown Voltage

The reverse bias breakdown voltage of the n+ -p junctions created on the wafers is related to the concentration of carriers on the more lightly doped side of the junction. The avalanche breakdown voltage is related to the doping concentration [12]. The breakdown characteristics of a p-n junction diode created in the lab are shown in *Figure 8*, in which it can seen that the breakdown voltage occurs at around –140V.

### Forward Deviations From Ideality

Two characteristics of a p-n junction might cause deviations from the ideal when the diode is forward biased. Both the bulk resistance and the ideality factor can affect the properties of the I-V characteristics of the device.

The diode current of a p-n junction is usually written as a function of the applied voltage as  $I = I_0 e^{qVd \, nkT} - 1$ , where  $I_0$  is the reverse saturation current, q is the charge on the electron, Vd is the diode voltage, n is the ideality factor, k is Boltzmann's constant, and T is the absolute temperature. This expression doesn't take into account the series resistance of the devices. The series resistance is a function of geometry, material resistance, and contact resistance. Taking the series resistance  $(r_s)$  into account, we may write the diode voltage as  $Vd = V - Ir_s$  where V is the applied voltage to the device [13]. The series resistance term in the equation accounts for the downward curvature of the data shown in the forward bias region in *Figure 7*.

#### Breakdown Voltage Measurement

Figure 8. Breakdown voltage measurement of a n+-p junction diode. The plot shows avalanche breakdown at about -140V.

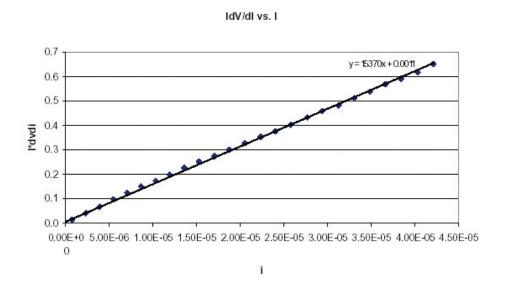

The conductance of the diode is defined as  $g_d = dI/dV$ . Using this expression and the two previous equations, it is straightforward to show that  $I/g_d = (nkT/q) + Irs$  which is a convenient form for determining the series resistance of the device. When  $I/g_d = (I \ dV/dI)$  is plotted vs. I, the resulting graph is a straight line with slope  $r_s$  and intercept nkT/q. *Figure 9* is such a plot generated from data measured on one of the n+-p junction diodes. The estimated series resistance of the diode obtained from a regression of I/gd vs. I is 15.37  $\pm 0.11k\Omega$ . The  $R^2$  for the regression of the diode in *Figure 8* is  $R^2 = 0.999$ . This value for  $r_s$  is extremely large. Typical p-n junction diodes have  $r_s$  values of a few ohms. This high series resistance results from both the large contact spacing (distance from the contacts to the junction) and the relatively low doping level of the p-side of the junction due to limitations imposed by the masks and mask aligner.

Figure 9. Plot of IdV/dI vs. I for a diode. The line is the linear regression fit to the data.

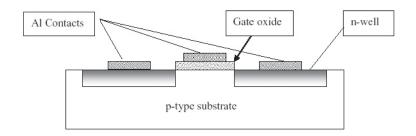

# 4) nMOSFETs

The nMOSFETs created in the process are made by doping two n-type wells in a p-type substrate, growing a 40nm gate oxide, and evaporating aluminum contacts for the drain, source, and gate, as shown in *Figure 10*. There are 20 FETs on each wafer, with channel lengths between 100µm and 250µm and widths between 500µm and 6000µm.

Figure 10. Layout of a p-channel enhancement MOSFET.

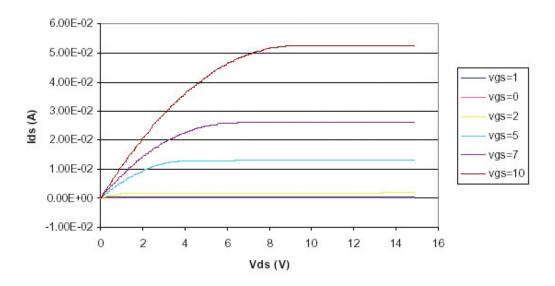

To measure the I–V characteristics of the MOSFETs, a DC voltage is applied to the gate by the data acquisition board while the value of the drain-to-source voltage ( $V_{DS}$ ) is swept with the Model 2400 SourceMeter instrument using user-defined limits and step values. During this time, the drain current  $I_D$  is measured, also with the Model 2400. This loop is performed for six user-defined gate voltage values, giving the characteristic curves for the FET, as shown in *Figure 11*. These data are available for export. *Figure 11* shows that the transistor has characteristics close to ideal, and that it is 'off' when the gate voltage ( $V_{GS}$ ) is zero, i.e., the current is about 32mA when  $V_{GS} = 0V$ .

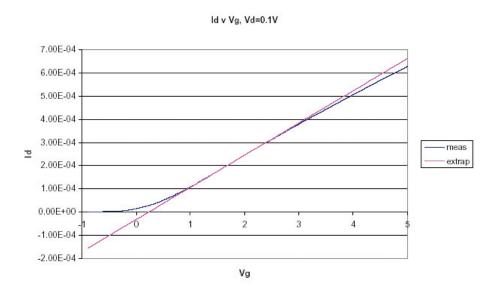

Although much can be inferred about the MOSFET fabrication process and operation from the curves shown in *Figure 11*, it's also beneficial to examine the threshold voltage characteristics of the device. In order to measure the threshold voltage of the FET, a small drain voltage is applied and the drain current is measured at each point of a user-defined gate voltage sweep [10, 14]. The small drain voltage ensures the device will operate in the linear region during the measurement. *Figure 12* shows an example of the I–V curve resulting from this measurement for the same device shown in *Figure 11*. To determine the threshold voltage, a line is drawn tangent to the curve at the point of inflection (maximum slope). The point of inflection of this curve, found from the maximum in the derivative of the curve, is at  $V_{GS} = 1.53V$ . The line tangent to the curve at this point will intercept the x-axis at  $V_{T}$ . The tangent curve is also shown in *Figure 12*. For this particular device, the threshold voltage is 0.24V.

#### Transistor Characteristic Curves

Figure 11. Characteristic curves for a MOSFET constructed in the lab.

Figure 12. Threshold voltage measurement for the device shown in Figure 9. A line is extrapolated through the point of inflection, tangent to the measured curve. The intercept of the extrapolated line with the x-axis is the threshold voltage, 0.24V.

#### **Discussion**

The semiconductor characterization tool developed here has demonstrated it is capable of a wide range of measurements on simple devices created in an entry-level undergraduate teaching cleanroom. The objective is to introduce students to the many exciting aspects of semiconductor fabrication and processing early stage in their scientific careers [15]. While the measurements described here are simple enough for students to perform, they are also sufficiently sophisticated that senior students taking such a laboratory course as a terminal course in their undergraduate education may develop a greater appreciation of details described in more advanced electronics courses.

# Acknowledgements

Keithley Instruments would like to thank Dr. Robert W. Hendricks and David T. Gray for using Keithley's Model 2400 SourceMeter instrument for their characterization tool. We are equally grateful for their generosity in allowing us to use excerpts from their work to encourage the development of characterization tools for student teaching labs. Their project was created under the auspices of the Virginia Microelectronics Consortium (VMEC), the Bradley Department of Electrical and Computer Engineering, and the Materials Science and Engineering Department at Virginia Polytechnic Institute and State University in Blacksburg, Virginia. Their work was supported by the National Science Foundation under CRCD grant 99-80282.

For further information on Virginia Tech's characterization system and for copies of the system software, contact Dr. Robert Hendricks at: robert.hendricks@vt.edu

#### References

- [1] C.T. Timmons, D.T. Gray, and R.W. Hendricks, "Process Development for an Undergraduate Microchip Fabrication Facility," in *Proc. 2001 ASEE Annual Conference*, Albuquerque, NM, 2001 (Available from the ASEE, Washington DC on CD-ROM.)

- [2] Keithley Instruments, Cleveland, OH (http://www.keithley.com/)

- [3] Signatone Corporation, Gilroy, CA (http://www.signatone.com/products/probingAccessories/4ptprobe.shtml

- [4] Designed by Dr. Carlos Suchicital of Virginia Tech and manufactured by Air Control, Inc. of Henderson, NC. (http://www.aircontrol-inc.com/)

- [5] Dell Corp, Austin, TX (http://www.dell.com/)

- [6] D.K. Schroder, *Semiconductor Material and Device Characterization*, 2nd ed., New York: Wiley-Interscience, 1998.

- [7] G.W. Neudeck, "The PN Junction Diode: Volume 3 in Modular Series on Solid State Devices," 2nd ed, Englewood Cliffs, NJ: Prentice-Hall, 1989.

- [8] R.F. Pierret, "Field Effect Devices: Volume 4 in Modular Series on Solid State Devices," 2nd ed., Englewood Cliffs, NJ: Prentice-Hall, 1990.

- [9] ASTM Standard F84-98, "Standard Test Method for Measuring Resistivity of Silicon Wafers With an In-Line Four-Point Probe," 1998 Annual Book of ASTM Standards, Am. Soc. Test. Mat., West Conshohocken, 1998.

- [10] ASTM Standard F617-95, "Standard Test Method for Measuring MOSFET Linear Threshold Voltage [Metric]," 1998 Annual Book of ASTM Standards, Am. Soc. Test. Mat., West Conshohocken, 1998.

- [11] Schroder, op. cit., p2 ff.

- [12] Neudeck, op. cit., p61 ff.

- [13] Schroder, op. cit., p. 200 ff.

- [14] Schroder, op. cit., p. 242 ff.

- [15] R.W. Hendricks, L.J. Guido, R.A. Heflin, and S.C. Sarin, "An Interdisciplinary Curriculum for Microelectronics," in Proc ASEE 2001 Annual Meeting (CD-ROM), ASEE, Washington, DC.

Specifications are subject to change without notice.

All Keithley trademarks and trade names are the property of Keithley Instruments, Inc. All other trademarks and trade names are the property of their respective companies.

Keithley Instruments, Inc. 28775 Aurora Road • Cleveland, Ohio 44139 • 440-248-0400 • Fax: 440-248-6168 1-888-KEITHLEY (534-8453) • www.keithley.com

© Copyright 2004 Keithley Instruments, Inc. Printed in the U.S.A.

No. 2524 0704